RISC-V

本文最后更新于:2023年5月11日 晚上

RISC-V

RISC-V 是多个 RV 指令集系列的总称,是一个开源的指令集,它遵循模块化设计理念,核心是一个名为 RV32I 的基础 ISA

RV32I 寄存器

| 通用寄存器 | 别名 | 功能 | 维护 |

|---|---|---|---|

| x0 | zero | 零寄存器 | N/A |

| x1 | ra | return adress | Caller |

| x2 | sp | 栈指针 | Callee |

| x3 | gp | 全局指针 | |

| x4 | tp | 线程指针 | |

| x5 | t0 | 临时寄存器or替代链接寄存器 | Caller |

| x6-x7 | t1-t2 | 临时寄存器 | Caller |

| x8 | s0/fp | 保存寄存器 | Callee |

| x9 | s1 | 保存寄存器 | Callee |

| x10-x11 | a0-a1 | 函数参数or返回值 | Caller |

| x12-17 | a2-a7 | 函数参数 | Caller |

| x18-x27 | s2-s11 | 保存寄存器 | Callee |

| x28-x31 | t3-t6 | 临时寄存器 |

控制状态寄存器CSR

| 通用寄存器 | 访问属性 | 功能 | |

|---|---|---|---|

| mvendorid | R | 厂商ID | |

| marchId | R | 体系结构id | |

| mimpid | R | 特点实现id | |

| mhartid | R | hart(硬件线程) id | |

| misa | R | 指令集架构信息 | |

| mcycle/mycycleh | R | 时钟周期计数器 | |

| cycle/ycycleh | R | 时钟周期计数器 | |

| minstret | R | 退休指令计数器 | |

| mstatus | RW | 状态控制 | |

| mie | RW | 中断使能 | |

| mip | R | 当前中断pengding位 | |

| mtvec | RW | 中断/异常矢量 | |

| mtval | RW | 异常和中断的补充信息(如异常指令,非法地址) | |

| mscratch | RW | 提供一个上下文保存寄存器 | |

| mepc | RW | 异常程序指针 | |

| mcause | R | 异常/中断原因 |

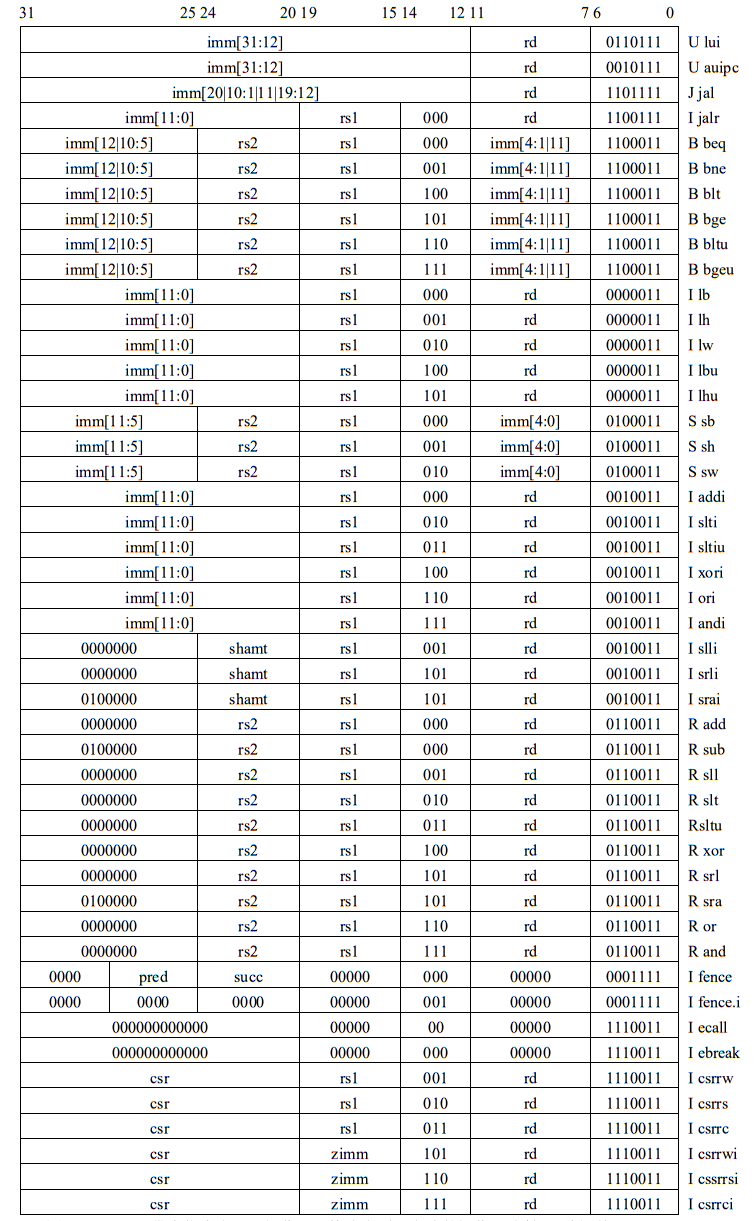

RV32I 基础指令(47)

指令格式

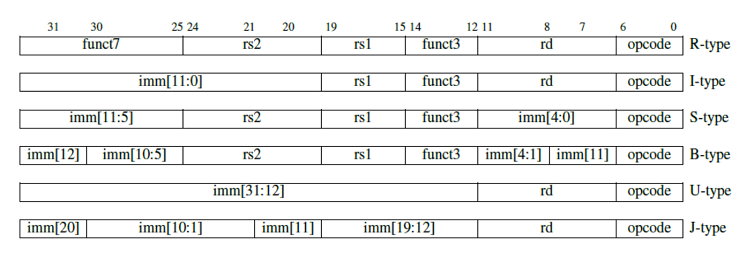

RISC-V ISA 是变长指令结构,但 RV32I 指令是固定长度,一条指令为32个bit,也就是4个字节,有6种指令格式:

- R 类型指令:用于寄存器-寄存器操作

- I 类型指令:用于短立即数和访存 load 操作

- S 类型指令:用于访存 store 操作

- B 类型指令:用于条件跳转操作

- U 类型指令:用于长立即数

- J 类型指令:用于无条件跳转

基础指令

RISC-V

https://shenysec.github.io/2023/04/23/RISC-V/